| VHDL<br>Description<br>of FSMs |  |

|--------------------------------|--|

| Dr DC<br>Hendry                |  |

FSM Block Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

### VHDL Descriptions of FSMs

Dr DC Hendry

March 15, 2006

▲□▶ ▲圖▶ ▲臣▶ ★臣▶ = 臣 = のへで

VHDL Descriptions of FSMs Dr DC

Hendry

FSM Block Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

### **1** FSM Block Diagram

### 2 VHDL Coding

- The State Register

- Next State and Output Combinational Logic

▲ロト ▲ □ ト ▲ □ ト ▲ □ ト ● ● の Q ()

### 3 Invoking Synthesis Tool Optimisations

## Block Diagram:

VHDL Descriptions of FSMs Dr DC Hendry

#### FSM Block Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

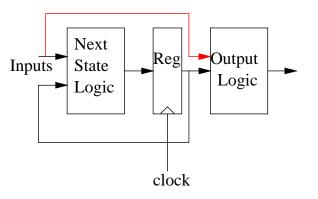

#### The block diagram of a Mealy FSM was:

### Block descriptions:

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

### The blocks of this design are:

State Register The state register has as input the clock signal, the next state from the next state logic on the D lines and normally an active low reset line. The output of the state register is the current state of the machine.

Next State Logic This combinational logic has as input the current state and the control inputs, its output is the next state.

Output Logic Another combinational logic block whose inputs are the current state (and only the current state for a Moore machine), and the control inputs (for a Mealy machine). The output is the output of the machine.

### VHDL Designs and FSMs

#### FSM Block Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations Each of the above blocks could be a separate design, but this is usually an overcomplication.

### VHDL Designs and FSMs

#### VHDL Descriptions of FSMs Dr DC Hendry

#### FSM Block Diagram

#### VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

- Each of the above blocks could be a separate design, but this is usually an overcomplication.

- One VHDL design is usually used which includes the state register and all combinational logic, and nothing else.

### VHDL Designs and FSMs

#### VHDL Descriptions of FSMs Dr DC Hendry

#### FSM Block Diagram

- VHDL Coding The State Register Next State and Output Combinational Logic

- Invoking Synthesis Tool Optimisations

- Each of the above blocks could be a separate design, but this is usually an overcomplication.

- One VHDL design is usually used which includes the state register and all combinational logic, and nothing else.

- By including only the FSM in a design the task of FSM analysis required by the synthesis tool for various optimisations is made simpler.

▲□▶▲□▶▲□▶▲□▶ □ のQで

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

#### VHDL Coding

The State Register Next State and Output Combinational Logi

Invoking Synthesis Tool Optimisations

#### User defined types make writing code easier and much more readable.

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

#### VHDL Coding

The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

- User defined types make writing code easier and much more readable.

- Such types can also greatly ease debugging of FSM designs as the simulator can show state names rather than state codes for an RTL simulation.

#### VHDL Descriptions of FSMs

Dr DC Hendry

#### FSM Block Diagram

#### VHDL Coding

The State Register Next State and Output Combinational Log

Invoking Synthesis Tool Optimisations

- User defined types make writing code easier and much more readable.

- Such types can also greatly ease debugging of FSM designs as the simulator can show state names rather than state codes for an RTL simulation.

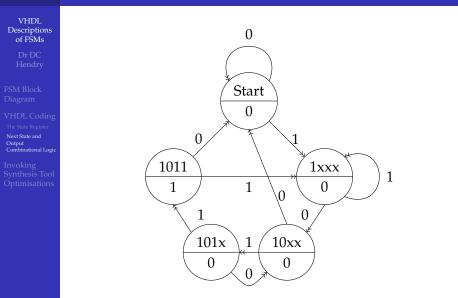

- For the sequence detector of the previous lecture:

signal current\_state, next\_state : statename;

#### VHDL Descriptions of FSMs

Dr DC Hendry

#### FSM Block Diagram

#### VHDL Coding

The State Register Next State and Output Combinational Log

Invoking Synthesis Tool Optimisations

- User defined types make writing code easier and much more readable.

- Such types can also greatly ease debugging of FSM designs as the simulator can show state names rather than state codes for an RTL simulation.

- Sor the sequence detector of the previous lecture:

< □ > < 同 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

The synthesis tool will later assign state codes.

FSM Block Diagram

VHDL Coding The State Register

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations • Should be edge triggered and include a reset line.

#### VHDL Descriptions of FSMs

Hendry

FSM Block Diagram

#### VHDL Coding The State Register

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

- Should be edge triggered and include a reset line.

- The reset line may be asynchronous or synchronous.

#### VHDL Descriptions of FSMs Dr DC

Hendry

FSM Block Diagram

#### VHDL Coding The State Register

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

- Should be edge triggered and include a reset line.

- The reset line may be asynchronous or synchronous.

- Reset lines are by convention (historical) active low, so names are typically rst\_n.

#### VHDL Descriptions of FSMs Dr DC

Hendry

FSM Block Diagram

#### VHDL Coding The State Register

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

- Should be edge triggered and include a reset line.

- The reset line may be asynchronous or synchronous.

- Reset lines are by convention (historical) active low, so names are typically rst\_n.

- On the active edge of the clock, copy next\_state into current\_state.

### State Register Code

#### VHDL Descriptions of FSMs

Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register Next State and Output

Invoking Synthesis Tool Optimisations Here is the code for the state register with an asynchronous active low reset line, using a process with a sensitivity list:

```

state_reg : process (clk, rst_n)

begin

if rst_n = '0' then

current_state <= start;

else if clk'event and clk = '1' then

current_state <= next_state;

end if;

end process state_reg;</pre>

```

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

VHDL Coding

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations The next state combinational logic for both a Mealy Machine and a Moore Machine has as input the current state and the control inputs.

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

- The next state combinational logic for both a Mealy Machine and a Moore Machine has as input the current state and the control inputs.

- As a process therefore, both the current state and the control inputs should be in the sensitivity list of the process.

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

- The next state combinational logic for both a Mealy Machine and a Moore Machine has as input the current state and the control inputs.

- As a process therefore, both the current state and the control inputs should be in the sensitivity list of the process.

- It is usual to assign a default next state at the start of the process, this can make code shorter (and so more readable).

▲□▶▲□▶▲□▶▲□▶ □ のQで

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

- The next state combinational logic for both a Mealy Machine and a Moore Machine has as input the current state and the control inputs.

- As a process therefore, both the current state and the control inputs should be in the sensitivity list of the process.

- It is usual to assign a default next state at the start of the process, this can make code shorter (and so more readable).

- A case statement based on the current state is usually simplest.

### The State Diagram ..

### Next State CL Process

#### VHDL Descriptions of FSMs

Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register Next State and

Output Combinational Logic

Invoking Synthesis Tool Optimisations next\_state\_logic: process (current\_state, a)

begin -- process next\_state\_logic

```

next_state \leq = start;

```

```

case current_state is

when start =>

if a = '0' then

next_state <= start;

else

next_state <= seen1;

end if;</pre>

```

### Next State CL Process

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations when seen1 =>

if a = '0' then

next\_state <= seen10;

else

next\_state <= seen1;

end if;</pre>

when seen10 =>

if a = '0' then

next\_state <= start;

else

next\_state <= seen101;

end if;</pre>

VHDL Descriptions of FSMs

Dr DC Hendry

FSM Block Diagram

```

VHDL Coding

The State Register

```

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations when seen101 =>

if a = '0' then

next\_state <= seen10;

else

next\_state <= success;

end if;</pre>

when success =>

if a = '0' then

next\_state <= start;

else

next\_state <= seen1;

end if;</pre>

when others => null; end case; end process next\_state\_logic;

# Output Logic

VHDL Descriptions of FSMs Dr DC

FSM Block Diagram

VHDL Coding The State Register

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations output\_logic: process (current\_state)

begin -- process output\_logic

if current\_state = success then

x <= '1';

else

x <= '0';

end if;

end process output\_logic;</pre>

#### Figure: Output Logic

### Simulation of Sequence Detector

VHDL Descriptions of FSMs

Dr DC Hendry

FSM Block Diagram

VHDL Coding

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations Use of these techniques does also aid in the debugging of state machines, use of an enumerated type for example makes reading a simulation plot much easier.

| Ci          | ursor = 49,935,000,000fs |        |            |            |              |             |              |         |        |            |          |       |      |

|-------------|--------------------------|--------|------------|------------|--------------|-------------|--------------|---------|--------|------------|----------|-------|------|

| Bas         | eline = 0                |        |            |            |              |             |              |         |        |            |          |       |      |

| ursor-Bas   | eline = 49,935,000,000fs |        | .000.000fs | 49,340,000 | .000fs 49.   | 360,000,000 | fs 49,000,00 | 0,000fs | s .    | 49,400,000 | .000fs   | . ŀ   | 49)  |

|             | clk                      | 0      |            |            |              |             |              |         |        |            |          |       |      |

| -2          | a                        | U      |            |            |              |             |              |         |        |            |          |       |      |

| <b>1</b> 20 | current_state            | seenl  | st) (seenl |            | (seenlU)(sta | urt (seer   | 11           | (seen]  | 10 )   | (seen101   | succes   | ss X  | star |

|             | next_state               | seen10 | seeni      | see≯       | (start       | (seen1      | See          | Xsta⊁   | Xsee≯} | success    | (see⊁)(: | start |      |

| 42          | rst_n                    | 1      |            |            |              |             |              | -       |        |            |          |       |      |

| - E>        | x                        | 0      |            |            |              |             |              |         |        |            |          |       |      |

|             |                          |        |            |            |              |             |              |         |        |            |          |       |      |

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations State Reduction. For certain state diagrams some states may be redundant. There are manual methods available to remove such states, these methods are time consuming however.

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations State Reduction. For certain state diagrams some states may be redundant. There are manual methods available to remove such states, these methods are time consuming however.

▲ロト ▲ □ ト ▲ □ ト ▲ □ ト ● ● の Q ()

State Assignment. Synthesis tools however do have algorithms available providing an approximate solution to this problem.

#### VHDL Descriptions of FSMs

Dr DC Hendry

- FSM Block Diagram

- VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

- State Reduction. For certain state diagrams some states may be redundant. There are manual methods available to remove such states, these methods are time consuming however.

- State Assignment. Synthesis tools however do have algorithms available providing an approximate solution to this problem.

- Once coded, the algorithms may be re-applied following a modification to the design. The designer is not therefore dissuaded from further development.

#### VHDL Descriptions of FSMs

Dr DC Hendry

- FSM Block Diagram

- VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations

- State Reduction. For certain state diagrams some states may be redundant. There are manual methods available to remove such states, these methods are time consuming however.

- State Assignment. Synthesis tools however do have algorithms available providing an approximate solution to this problem.

- Once coded, the algorithms may be re-applied following a modification to the design. The designer is not therefore dissuaded from further development.

- In PKS, and in most tools, such optimisations are controlled by additional *attributes*.

VHDL Descriptions of FSMs Dr DC

FSM Block Diagram VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations Here is part of the code of the sequence detector design that I actually used:

library ambit; use ambit.attributes.all;

architecture rtl of detector is

type state\_name is (start, seen1, seen10, seen101, success); signal current\_state, next\_state : state\_name; attribute STATE\_VECTOR of current\_state : signal is true ; attribute ENCODING of current\_state : signal is "one\_hot";

begin -- rtl

#### VHDL Descriptions of FSMs Dr DC

#### FSM Block Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations • Cadence supplies a library called ambit that supplies the attributes package.

#### VHDL Descriptions of FSMs Dr DC Hendry

- FSM Block Diagram

- VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations • Cadence supplies a library called ambit that supplies the attributes package.

▲ロト ▲ □ ト ▲ □ ト ▲ □ ト ● ● の Q ()

**2** These attributes are therefore vendor dependent.

#### VHDL Descriptions of FSMs Dr DC Hendry

- FSM Block Diagram

- VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations  Cadence supplies a library called ambit that supplies the attributes package.

▲ロト ▲ □ ト ▲ □ ト ▲ □ ト ● ● の Q ()

- In the set of the s

- To have PKS extract all states in an FSM use the command:

do\_build\_generic -extract\_fsm

#### VHDL Descriptions of FSMs Dr DC Hendry

- FSM Block Diagram

- VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations  Cadence supplies a library called ambit that supplies the attributes package.

▲ロト ▲ □ ト ▲ □ ト ▲ □ ト ● ● の Q ()

- In the set of the s

- To have PKS extract all states in an FSM use the command:

do\_build\_generic -extract\_fsm

and then report the states with: report\_fsm -state

#### VHDL Descriptions of FSMs

Dr DC Hendry

FSM Block Diagram VHDL Codin <sup>The State Register</sup>

Output Combinational Logi

Invoking Synthesis Tool Optimisations The attribute ENCODING of the signal current\_state directs the synthesis tool to use a certain algorithm for coding of the state code. Some of the supported options are:

binary Use a sequential binary coding, 00, 01, 10, 11 etc.

#### VHDL Descriptions of FSMs

Dr DC Hendry

FSM Block Diagram VHDL Codin The State Register

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations The attribute ENCODING of the signal current\_state directs the synthesis tool to use a certain algorithm for coding of the state code. Some of the supported options are:

binary Use a sequential binary coding, 00, 01, 10, 11 etc.

▲□▶▲□▶▲□▶▲□▶ □ のQで

one\_hot Use a one-hot encoding (discussed later).

#### VHDL Descriptions of FSMs

Dr DC Hendry

FSM Block Diagram VHDL Codir <sup>The State Register</sup>

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations The attribute ENCODING of the signal current\_state directs the synthesis tool to use a certain algorithm for coding of the state code. Some of the supported options are:

binary Use a sequential binary coding, 00, 01, 10, 11 etc.

one\_hot Use a one-hot encoding (discussed later). area Use an encoding which minimises logic area (heuristic).

▲□▶▲□▶▲□▶▲□▶ □ のQで

#### VHDL Descriptions of FSMs

Dr DC Hendry

FSM Block Diagram VHDL Codii

Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations The attribute ENCODING of the signal current\_state directs the synthesis tool to use a certain algorithm for coding of the state code. Some of the supported options are:

binary Use a sequential binary coding, 00, 01, 10, 11 etc.

one\_hot Use a one-hot encoding (discussed later).

area Use an encoding which minimises logic area (heuristic).

timing Use an encoding for least propagation delay (heuristic).

< □ > < 同 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

# One Hot Encoding

VHDL Descriptions of FSMs

> Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations  One-hot encoding uses one flip-flop per state of the machine, so more flip-flops are required.

# One Hot Encoding

#### VHDL Descriptions of FSMs

Dr DC Hendry

FSM Blocl Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations One-hot encoding uses one flip-flop per state of the machine, so more flip-flops are required.

▲ロト ▲ □ ト ▲ □ ト ▲ □ ト ● ● の Q ()

One one flip-flop has its Q set at a time (the hot flip-flop), all others are at 0.

# One Hot Encoding

#### VHDL Descriptions of FSMs

Dr DC Hendry

FSM Block Diagram

VHDL Coding The State Register Next State and Output Combinational Logic

Invoking Synthesis Tool Optimisations  One-hot encoding uses one flip-flop per state of the machine, so more flip-flops are required.

▲ロト ▲ □ ト ▲ □ ト ▲ □ ト ● ● の Q ()

One one flip-flop has its Q set at a time (the hot flip-flop), all others are at 0.

#### Resultant state encoding:

| State   | Code  |

|---------|-------|

| start   | 10000 |

| seen1   | 01000 |

| seen10  | 00100 |

| seen101 | 00010 |

| success | 00001 |