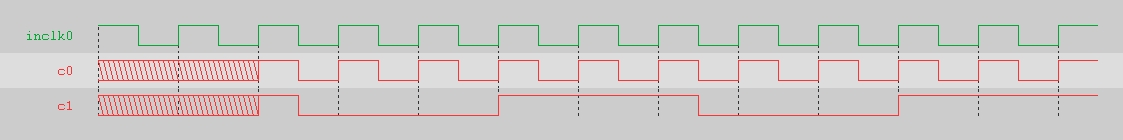

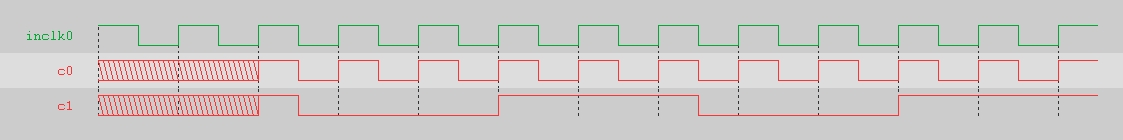

The following waveforms show the behavior of altpll megafunction for the chosen set of parameters in design EQ_PLL_50.vhd. The design EQ_PLL_50.vhd has Cyclone II PLL_TYPE pll configured in NORMAL mode The primary clock input to the PLL is INCLK0, with clock period 20000 ps.